SystemVerilog Assertions

Table of Contents

Assertions are primarily used to validate the behavior of a design. An assertion is a check embedded in design or bound to a design unit during the simulation. Warnings or errors are generated on the failure of a specific condition or sequence of events.

Assertions are used to,

- Check the occurrence of a specific condition or sequence of events.

- Provide functional coverage.

There are two kinds of assertions:

- Immediate Assertions

- Concurrent Assertions

Immediate Assertions:

Immediate assertions check for a condition at the current simulation time.

An immediate assertion is the same as an if..else statement with assertion control. Immediate assertions have to be placed in a procedural block definition.

Syntax

label: assert(expression) action_block;

- The optional statement label (identifier and colon) creates a named block around the assertion statement

- The action block is executed immediately after the evaluation of the assert expression

- The action_block specifies what actions are taken upon success or failure of the assertion

action_block;

pass_statement; else fail_statement;

- The pass statement is executed if the expression evaluates to true

- The statement associated with else is called a fail statement and is executed if the expression evaluates to false

- Both pass and fail statements are optional

- Since the assertion is a statement that something must be true, the failure of an assertion shall have a severity associated with it. By default, the severity of an assertion failure is an error.

- Other severity levels can be specified by including one of the following severity system tasks in the fail statement:

- $fatal is a run-time fatal.

- $error is a run-time error.

- $warning is a run-time warning, which can be suppressed in a tool-specific manner.

- $info indicates that the assertion failure carries no specific severity.

- If an assertion fails and no else clause is specified, the tool shall, by default call $error.

Below are the different forms of immediate assertion syntax with and without optional items

//With Pass and Fail statement; Fail verbosity info;

assert(expression) $display(“expression evaluates to true”); else $display(“expression evaluates to false”);

//Only With Pass statement;

assert(expression) $display(“expression evaluates to true”);

//With Pass and Fail statement; Fail verbosity fatal;

assert(expression) $display(“expression evaluates to true”); else $fatal(“expression evaluates to false”);

//Only With Fail statement; Multiple statements in Faile condition and Fail verbosity fatal;

assert(expression)

else begin

…….

…….

$fatal(“expression evaluates to false”);

end

//Only With Fail statement; Fail verbosity warning;

assert(expression) else $warning(“expression evaluates to false”);

//With Label and Fail statement; Fail verbosity warning;

label: assert(expression) else $warning(“expression evaluates to false”);

Immediate assertion example

Below is the simple immediate assertion,

always @(posedge clk) assert (a && b);

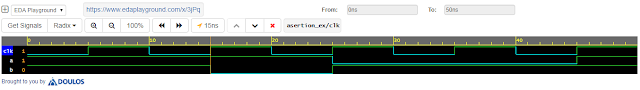

Below is the wave diagram for the above assertion.

Condition (a && b) will be checked at every posedge of the clock, failure in the condition leads to an assertion failure.

module asertion_ex;

bit clk,a,b;

//clock generation

always #5 clk = ~clk;

//generating 'a'

initial begin

a=1;

b=1;

#15 b=0;

#10 b=1;

a=0;

#20 a=1;

#10;

$finish;

end

//Immediate assertion

always @(posedge clk) assert (a && b);

endmodule

Simulator Output

ncsim: *E,ASRTST (./testbench.sv,23): (time 15 NS) Assertion asertion_ex.__assert_1 has failed ncsim: *E,ASRTST (./testbench.sv,23): (time 25 NS) Assertion asertion_ex.__assert_1 has failed ncsim: *E,ASRTST (./testbench.sv,23): (time 35 NS) Assertion asertion_ex.__assert_1 has failed Simulation complete via $finish(1) at time 55 NS + 0

Concurrent Assertions:

Concurrent assertions check the sequence of events spread over multiple clock cycles.

- The concurrent assertion is evaluated only at the occurrence of a clock tick

- The test expression is evaluated at clock edges based on the sampled values of the variables involved

- It can be placed in a procedural block, a module, an interface or a program definition

c_assert: assert property(@(posedge clk) not(a && b));

The Keyword differentiates the immediate assertion from the concurrent assertion is “property.”