Introduction to UVM Register Model

The UVM Register Layer provides a standard base class libraries that enable users to implement the object-oriented model to access the DUT registers and memories. UVM Register Layer is also referred to as UVM Register Abstraction Layer (UVM RAL).

For register access, can’t we proceed without RAL?

Yes, we can. But as mentioned above, RAL provides a set of base classes and methods with a set of rules which easies the effort required for register access.

Advantages of UVM RAL

The advantages of UVM RAL Model are,

- Provides high-level abstraction for reading and writing DUT registers. i.e, registers can be accessed with its names

- UVM provides a register test sequence library containing predefined test cases these can be used to verify the registers and memories

- register layer classes support front-door and back-door access

- Design registers can be accessed independently of the physical bus interface. i.e by calling read/write methods

- The register model can be accessed from multiple concurrent threads. it internally serializes the access to the register.

- Reusability, RAL packages can be directly reused in other environments

- Uniformity, Defines the set of rules or methodology on register access, which can be followed across the industry

- Automated RAL model generations, Tools or open-source scripts are available for RAL Model generation

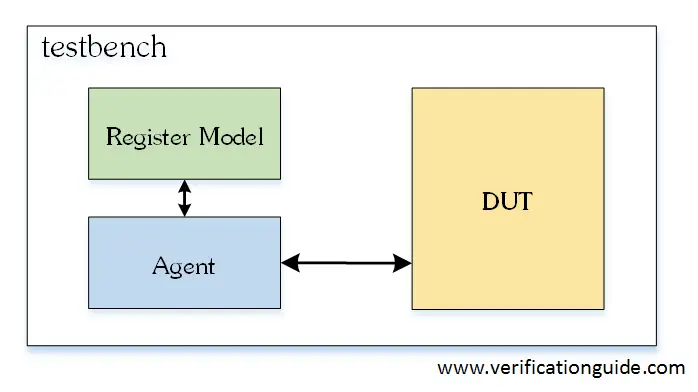

Below block diagram shows using RAL in the verification testbench.

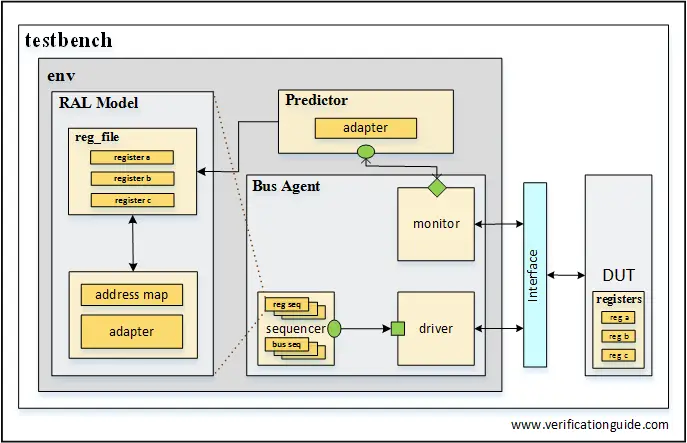

The below diagram shows the detailed components and connection of RAL with testbench.

UVM RAL Components and Methods will be described in the upcoming sessions.

❮ Previous Next ❯