UVM TestBench

Table of Contents

UVM testbenches are constructed by extending uvm classes.

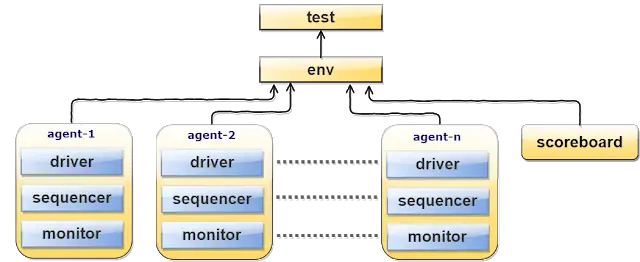

UVM testbench hierarchy

Below is the typical UVM testbench hierarchy diagram.

Role of each testbench element is explained below,

UVM test

The test is the topmost class. the test is responsible for,

- configuring the testbench.

- Initiate the testbench components construction process by building the next level down in the hierarchy ex: env.

- Initiate the stimulus by starting the sequence.

UVM Environment

Env or environment: The environment is a container component for grouping higher level components like agent’s and scoreboard.

UVM Agent

UVM agent groups the uvm_components specific to an interface or protocol.

example: groups the components associated with BFM(Bus Functional Model).\

The components of an agent are,

UVM Sequence item

The sequence-item defines the pin level activity generated by agent (to drive to DUT through the driver) or the activity has to be observed by agent (Placeholder for the activity monitored by the monitor on DUT signals).

UVM Driver

Responsible for driving the packet level data inside sequence_item into pin level (to DUT).

UVM Sequence

Defines the sequence in which the data items need to be generated and sent/received to/from the driver.

UVM Sequencer

Responsible for routing the data packet’s(sequence_item) generated in sequence to the driver or vice verse.

UVM Monitor

Observes pin level activity on interface signals and converts into packet level which is sent to components such as scoreboards.

UVM Scoreboard

Receives data item’s from monitor’s and compares with expected values.

expected values can be either golden reference values or generated from the reference model.

For a detailed explanation of each component and methods refer to UVM Tutorial.

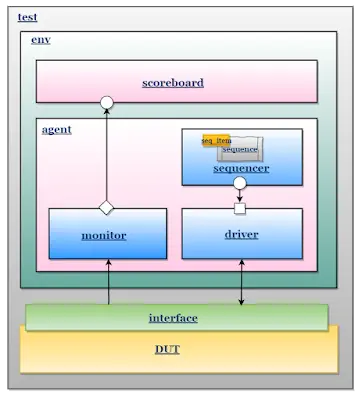

UVM TestBench Block Diagram

- UVM TestBench Block Diagram with a single agent.

- UVM TestBench Block Diagram with multiple agents and multiple instances of each